#### **DESCRIPTION**

The AO1007 offers low offset and long-term stability by means of a low noise and high voltage operational amplifier circuit. For most applications, external components are not required for offset nulling and frequency compensation.

The AO1007 has a gain-bandwidth product of 2MHz, a slew rate of 1.2V/us and a quiescent current of 1mA at wide power supply range.

The AO1007 is designed to provide optimal performance in low noise systems. It provides rail-to-rail output swing into heavy loads.

The AO1007 is available in SOP8 package.

### ORDERING INFORMATION

| Package Type                                 | Part Number |            |  |  |

|----------------------------------------------|-------------|------------|--|--|

| SOP8                                         | 1.40        | AO1007M8R  |  |  |

| SPQ: 4,000pcs/Reel                           | M8          | AO1007M8VR |  |  |

| Note  V: Halogen free Package R: Tape & Reel |             |            |  |  |

| AiT provides all RoHS products               |             |            |  |  |

### **FEATURES**

- No External Components Required

- Supply Voltage Range: 3.3V to 32V

- Low Offset Voltage: ±0.2mV (TYP)

- Low Bias Current: ±10pA (TYP)

- Gain Bandwidth Product: 2MHz

- Low Quiescent Current: 1mA (TYP)

- Overload Recovery Time: 1.6us

- Temperature: -40°C to +125°C

## **APPLICATION**

- Wireless Base Station Control Circuits

- Optical Network Control Circuits

- Instrumentation

- Sensors and Controls

- Precision Filters

- Cellular and Cordless Phones

- Photodiode Amplification

- A/D Converters

- Laptops and PDAs

- Medical and Industrial Instrumentation

### TYPICAL APPLICATION

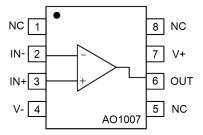

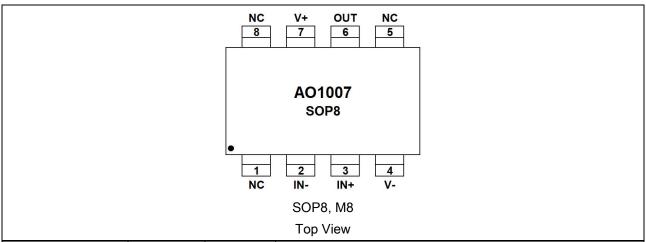

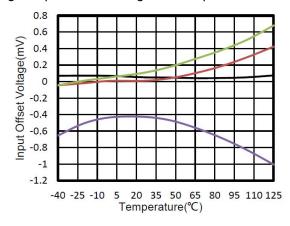

# PIN DESCRIPTION

| Pin#  | Symbol            | I/O <sup>(1)</sup> | Functions                                     |  |

|-------|-------------------|--------------------|-----------------------------------------------|--|

| SOP8  |                   |                    |                                               |  |

| 1,5,8 | NC <sup>(2)</sup> | -                  | No internal connection (can be left floating) |  |

| 2     | IN-               | I                  | Negative (inverting) input                    |  |

| 3     | IN+               | I                  | Positive (noninverting) input                 |  |

| 4     | V-                | -                  | Negative (lowest) power supply                |  |

| 6     | OUT               | 0                  | Output                                        |  |

| 7     | V+                | -                  | Positive (highest) power supply               |  |

<sup>(1)</sup> I = Input, O = Output.

<sup>(2)</sup> There is no internal connection. Typically, GND is the recommended connection to a heat spreading plane

## **ABSOLUTE MAXIMUM RATINGS**

Over operating free-air temperature range (unless otherwise noted)

| Over operating nee-an temperatu                      |                                 |                         |                      |

|------------------------------------------------------|---------------------------------|-------------------------|----------------------|

| Vs=(V+) - (V-), Supply Voltage                       |                                 |                         | 36V                  |

| Signal Input Pin Voltage (1)                         |                                 |                         | (V-)-0.3V~(V+) +0.3V |

| Signal Output Pin Voltage (2)                        |                                 |                         | (V-)-0.3V~(V+) +0.3V |

| Signal Input Pin Current (1)                         |                                 |                         | ±10mA                |

| Signal Output Pin Current (2)                        |                                 |                         | ±10mA                |

| θ <sub>JA</sub> , Package Thermal Impedanc           | e (3)                           | SOP8                    | 110°C/W              |

| T <sub>A</sub> , Operating Range                     |                                 | -40°C ~ +125°C          |                      |

| T <sub>J</sub> , Junction Temperature <sup>(4)</sup> |                                 | -40°C ~ +150°C          |                      |

| T <sub>STG</sub> , Storage Temperature               |                                 | -65°C ~ +150°C          |                      |

| ESD Susceptibility                                   |                                 |                         |                      |

|                                                      | Huma                            | n-body model (HBM), per | ±2000V               |

| Al                                                   |                                 | ESDA/JEDEC JS-001(5)    | ±2000V               |

| V <sub>(ESD)</sub> , Electrostatic Discharge         | Charged-device model (CDM), per |                         | +4000/               |

|                                                      | ANSI/ESDA/JEDEC JS-002(6)       |                         | ±1000V               |

| Machine Model (MM)                                   |                                 | ±200V                   |                      |

Stresses above may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated in the Electrical Characteristics are not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

- (1) Input terminals are diode-clamped to the power-supply rails. Input signals that can swing more than 0.3V beyond the supply rails should be current-limited to 10mA or less.

- (2) Output terminals are diode-clamped to the power-supply rails. Output signals that can swing more than 0.3V beyond the supply rails should be current-limited to ±10mA or less.

- (3) The package thermal impedance is calculated in accordance with JESD-51.

- (4) The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $R_{\theta JA}$ , and TA. The maximum allowable power dissipation at any ambient temperature is PD =  $(J_{J(MAX)} T_A) / R_{\theta JA}$ . All numbers apply for packages soldered directly onto a PCB.

- (5) JEDEC document JEP155 states that 500 V HBM allows safe manufacturing with a standard ESD control process.

- (6) JEDEC document JEP157 states that 250 V CDM allows safe manufacturing with a standard ESD control process.

### **Recommended Operating Conditions**

Over operating free-air temperature range (unless otherwise noted)

|                                  |               | Min.  | Non. | Max. | Unit |

|----------------------------------|---------------|-------|------|------|------|

| Supply valtage Va- (VI)          | Single-supply | 3.3   | 1    | 32   | \ /  |

| Supply voltage , Vs= (V+) - (V-) | Dual-supply   | ±1.65 | -    | ±16  | V    |

# **ELECTRICAL CHARACTERISTICS**

$T_A$ =+25°C,  $V_S$ =3.3V to 32V,  $R_L$ =10k $\Omega$  connected to  $V_S$ /2, and  $V_{OUT}$ = $V_S$ /2,  $V_{CM}$ = $V_S$ /2,unless otherwise noted (1)

| Parameter                   | Symbol              | Conditions                                              |               |      | Typ. (3) |        | Units |

|-----------------------------|---------------------|---------------------------------------------------------|---------------|------|----------|--------|-------|

| POWER SUPPLY                |                     |                                                         |               | •    |          |        |       |

| Operating Voltage Range     | Vs                  |                                                         |               | 3.3  | -        | 32     | V     |

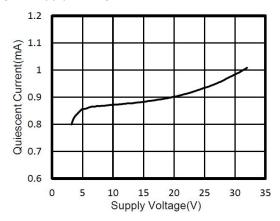

| Quiescent Current           | 1-                  | $V_S$ =±2.5 $V$ , $I_O$ =0 $mA$                         |               | -    | 1.0      | 1.5    | mΛ    |

| Per Amplifier               | ΙQ                  | V <sub>S</sub> =±16V, I <sub>O</sub> =0mA               |               | -    | 1.4      | 1.8    | mA    |

| Power-Supply                | PSRR                | V <sub>S</sub> =5V to 32V                               |               | 82   | 100      |        | dB    |

| Rejection Ratio             | FORK                | VS=3V tO 32V                                            |               | 02   | 100      |        | uБ    |

| INPUT                       |                     |                                                         |               |      |          |        |       |

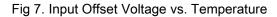

|                             |                     | V <sub>S</sub> =5V, V <sub>CM</sub> =V <sub>S</sub> /2  | +25℃          | -0.4 | ±0.2     | 0.4    |       |

| Input Offset Voltage        | Vos                 | V3 0 V, V CIVI V 3/2                                    | -40°C ~+125°C | -    | ±1.0     | -      | mV    |

| input onset voltage         | <b>V</b> 03         | V <sub>S</sub> =32V, V <sub>CM</sub> =V <sub>S</sub> /2 | +25°C         | -0.9 | ±0.4     | 0.9    | IIIV  |

|                             |                     | V3 02 V, VCIVI V3/2                                     | -40°C ~+125°C | -    | ±1.0     | -      |       |

| Input Offset Voltage        | Vos Tc              | V <sub>CM</sub> = V <sub>S</sub> /2                     |               | _    | ±5.0     | -      | μV/°C |

| Average Drift               | VOSTC               | -40°C ~+125°C                                           |               | -    |          |        |       |

| Input Bias Current (4)(5)   | lв                  | V <sub>CM</sub> = 0V                                    |               | -    | ±10      | 1      | pА    |

| Input Offset Current (4)    | los                 | V <sub>CM</sub> = 0V                                    |               | -    | ±10      | ı      | pА    |

| Common-Mode                 | $V_{CM}$            |                                                         |               | (V-) | -        | (V+)-2 | V     |

| Voltage Range               | V CM                |                                                         |               |      |          |        |       |

| Common-Mode                 | CMRR                | V <sub>S</sub> = ±16V                                   |               | 87   | 115      |        | dB    |

| Rejection Ratio             | Civilata            | V <sub>CM</sub> =(V-) to (V+)-2V                        |               | 01   | 115      | -      | ub    |

| OUTPUT                      |                     |                                                         |               |      |          |        |       |

| Open-Loop Voltage Gain      | A <sub>OL</sub>     | $R_L$ =10K $\Omega$<br>$V_O$ =(V-)+0.5V to (V+)-0.5V    |               | 117  | 150      | -      | dB    |

| Open-Loop Vollage Gain      |                     |                                                         |               |      |          |        |       |

| Output Swing from Rail      | Vон                 | $V_S=\pm 16V$ , $R_L=10K\Omega$                         |               | 15.7 | -        | -      | V     |

| - Catpat Ching II chin tail | V <sub>OL</sub>     |                                                         |               | -    | -        | -15.7  |       |

| Output Source               | lanua.              |                                                         |               | 65   | 142      | _      |       |

| Current (6) (7)             | I <sub>SOURCE</sub> | Vs=10V                                                  |               | 0.5  | 174      | -      | mA    |

| Output Sink Current (6) (7) | I <sub>SINK</sub>   |                                                         |               | 45   | 103      | -      |       |

| Capacitive Load Drive       | C <sub>LOAD</sub>   |                                                         |               | -    | 1        | -      | nF    |

AO1007

OP AMPLIFIER HIGH VOLTAGE SINGLE PRECISION OP

| Parameter              | Symbol             | Conditions                                       | Min. (2) | Typ. (3) | Max. (2) | Units       |

|------------------------|--------------------|--------------------------------------------------|----------|----------|----------|-------------|

| FREQUENCY RESPONSI     | FREQUENCY RESPONSE |                                                  |          |          |          |             |

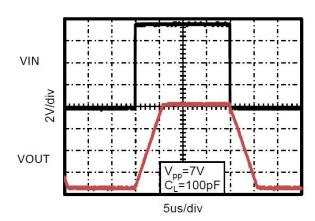

| Slew Rate (8)          | SR                 | G=+1, C <sub>L</sub> =100pF                      | -        | 1.2      | -        | V/µs        |

| Gain-Bandwidth Product | GBW                | G=10, R <sub>L</sub> =10KΩ, VPPvin=50mV          | -        | 2.0      | -        | MHz         |

| Settling Time,0.1%     | ts                 | V <sub>S</sub> =±16V, G=+1,                      | -        | 8.0      | -        |             |

|                        |                    | C <sub>L</sub> =100pF, Step=7V                   |          |          |          | μs          |

| Overload Recovery Time | tor                | V <sub>IN</sub> x Gain ≥ V <sub>S</sub> , G=-100 | -        | 1.6      | ı        | μs          |

| Turn on Time           | ton                | G=1                                              | -        | 75       | ı        | μs          |

| NOISE                  |                    |                                                  |          |          |          |             |

| Input Voltage Noise    | E <sub>N</sub>     | f = 0.1Hz to 10Hz, V <sub>S</sub> =±2.5V         | -        | 4.3      | -        | μVрр        |

| Input Voltage Noise    |                    | f =1KHz                                          |          | 14       |          | nV/         |

| Density (4)            | en                 |                                                  | -        | 14       | -        | $\sqrt{Hz}$ |

- (1) Electrical table values apply only for factory testing conditions at the temperature indicated. Factory testing conditions result in very limited self-heating of the device.

- (2) Limits are 100% production tested at 25°C. Limits over the operating temperature range are ensured through correlations using statistical quality control (SQC) method.

- (3) Typical values represent the most likely parametric norm as determined at the time of characterization. Actual typical values may vary over time and will also depend on the application and configuration.

- (4) This parameter is ensured by design and/or characterization and is not tested in production.

- (5) Positive current corresponds to current flowing into the device.

- (6) The maximum power dissipation is a function of  $T_{J(MAX)}$ ,  $R_{\theta JA}$ , and  $T_A$ . The maximum allowable power dissipation at any ambient temperature is PD =  $(T_{J(MAX)} T_A) / R_{\theta JA}$ . All numbers apply for packages soldered directly onto a PCB.

- (7) Short circuit test is a momentary test.

- (8) Number specified is the slower of positive and negative slew rates.

## TYPICAL PERFORMANCE CHARACTERISTICS

$T_A = +25$ °C,  $V_S = \pm 16$ V, unless otherwise noted.

Fig 1. Supply Voltage vs. Quiescent Current

Fig 3. Large-Signal Step Response

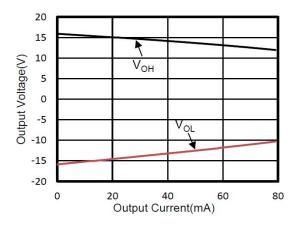

Fig 5. Output Voltage vs. Output Current

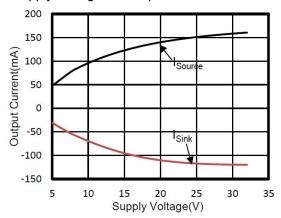

Fig 2. Supply Voltage vs. Output Current

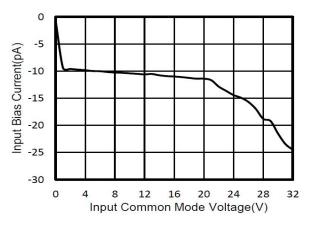

Fig 4. Input Bias Current vs. Input Common Mode Voltage

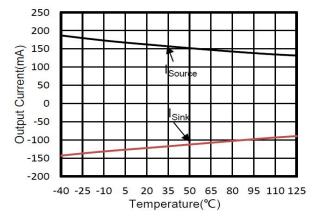

Fig 6. Output Current vs. Temperature

# **BLOCK DIAGRAM**

### **DETAILED INFORMATION**

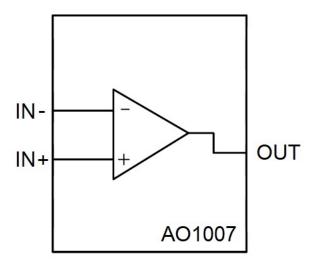

The AO1007 operates from either a single 3.3V to 32V supply or dual ±1.65V to ±16V supplies. For single-supply operation, bypass the power supply V+ with a 0.1µF ceramic capacitor which should be placed close to the V+ pin. For dual-supply operation, both the V+ and the V- supplies should be bypassed to ground with separate 0.1µF ceramic capacitors. 10µF tantalum capacitor can be added for better performance. Good PC board layout techniques optimize performance by decreasing the amount of stray capacitance at the operational amplifier's inputs and output. To decrease stray capacitance, minimize trace lengths and widths by placing external components as close to the device as possible. Use surface-mount components whenever possible. For the operational amplifier, soldering the part to the board directly is strongly recommended. Try to keep the high frequency current loop area small to minimize the EMI (electromagnetic interference).

Fig 8. Amplifier with Bypass Capacitors

### Grounding

A ground plane layer is important for AO1007 circuit design. The length of the current path in an inductive ground return will create an unwanted voltage noise. Broad ground plane areas will reduce the parasitic inductance.

#### Input-to-Output Coupling

To minimize capacitive coupling, the input and output signal traces should not be in parallel. This helps reduce unwanted positive feedback.

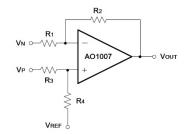

#### **Differential Amplifier**

The circuit shown in Fig 9 performs the difference function. If the resistor ratios are equal  $(R_4/R_3 = R_2/R_1)$ , then  $V_{OUT} = (V_P - V_N) \times R_2/R_1 + V_{REF}$ .

Fig 9. Differential Amplifier

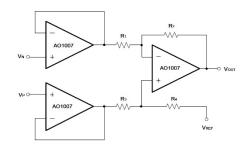

#### **Instrumentation Amplifier**

The circuit in Fig 10 performs the same function as that in Fig 9 but with a high input impedance.

Fig 10. Instrumentation Amplifier

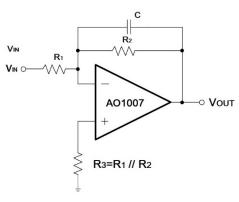

#### **Active Low-Pass Filter**

The low-pass filter shown in Fig 11 has a DC gain of (-R2/R1) and the -3dB corner frequency is  $1/2\pi R_2C$ . Make sure the filter bandwidth is within the bandwidth of the amplifier. Feedback resistors with large values can couple with parasitic capacitance and cause undesired effects such as ringing or oscillation in high-speed amplifiers. Keep resistor values as low as possible and consistent with output loading consideration

Fig 11. Active Low-Pass Filter

#### **Layout Guidelines**

Attention to good layout practices is always recommended. Keep traces short. When possible, use a PCB ground plane with surface-mount components placed as close to the device pins as possible. Place a 0.1uF capacitor closely across the supply pins.

These guidelines should be applied throughout the analog circuit to improve performance and provide benefits such as reducing the EMI susceptibility.

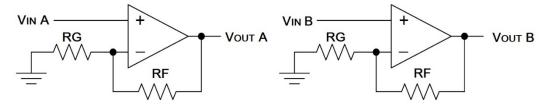

#### Layout Example

Fig 12. Schematic Representation

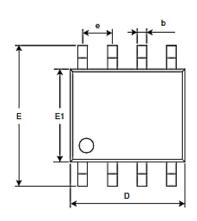

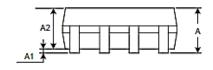

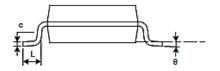

# PACKAGE INFORMATION

Dimension in SOP8 (Unit: mm)

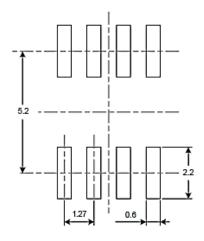

RECOMMENDED LAND PATTERN

| Cymah al | Millimeters |       |  |  |

|----------|-------------|-------|--|--|

| Symbol   | Min         | Max   |  |  |

| Α        | 1.350       | 1.750 |  |  |

| A1       | 0.100       | 0.250 |  |  |

| A2       | 1.350       | 1.550 |  |  |

| b        | 0.330       | 0.510 |  |  |

| С        | 0.170       | 0.250 |  |  |

| D        | 4.800       | 5.000 |  |  |

| е        | 1.270 BSC   |       |  |  |

| Е        | 5.800       | 6.200 |  |  |

| E1       | 3.800       | 4.000 |  |  |

| L        | 0.400       | 1.270 |  |  |

| θ        | 0° 8°       |       |  |  |

AO1007

OP AMPLIFIER HIGH VOLTAGE SINGLE PRECISION OP

## **IMPORTANT NOTICE**

AiT Semiconductor Inc. (AiT) reserves the right to make changes to any its product, specifications, to discontinue any integrated circuit product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

AiT Semiconductor Inc. 's integrated circuit products are not designed, intended, authorized, or warranted to be suitable for use in life support applications, devices or systems or other critical applications. Use of AiT products in such applications is understood to be fully at the risk of the customer. As used herein may involve potential risks of death, personal injury, or server property, or environmental damage. In order to minimize risks associated with the customer's applications, the customer should provide adequate design and operating safeguards.

AiT Semiconductor Inc. assumes to no liability to customer product design or application support. AiT warrants the performance of its products of the specifications applicable at the time of sale.